全志R16多核架构简介

1. 多核架构

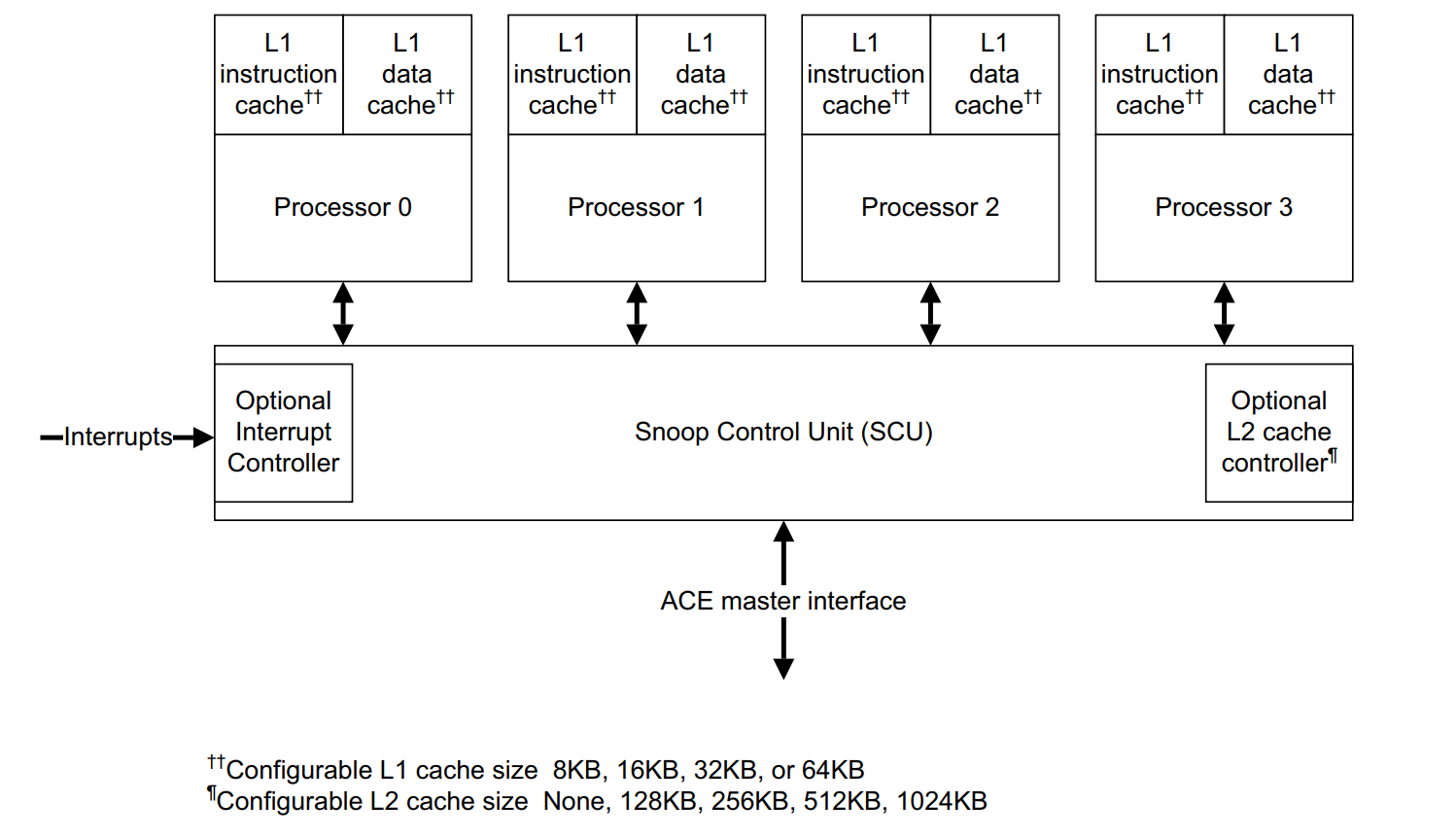

在学习SylixOS多核BSP开发之前,我们有必要先简单了解下多核架构的基本知识。全志R16是Arm Cortex-A7结构的多核处理器,从Cortex-A7 MPCore手册中我们可以看到多核的基本架构:

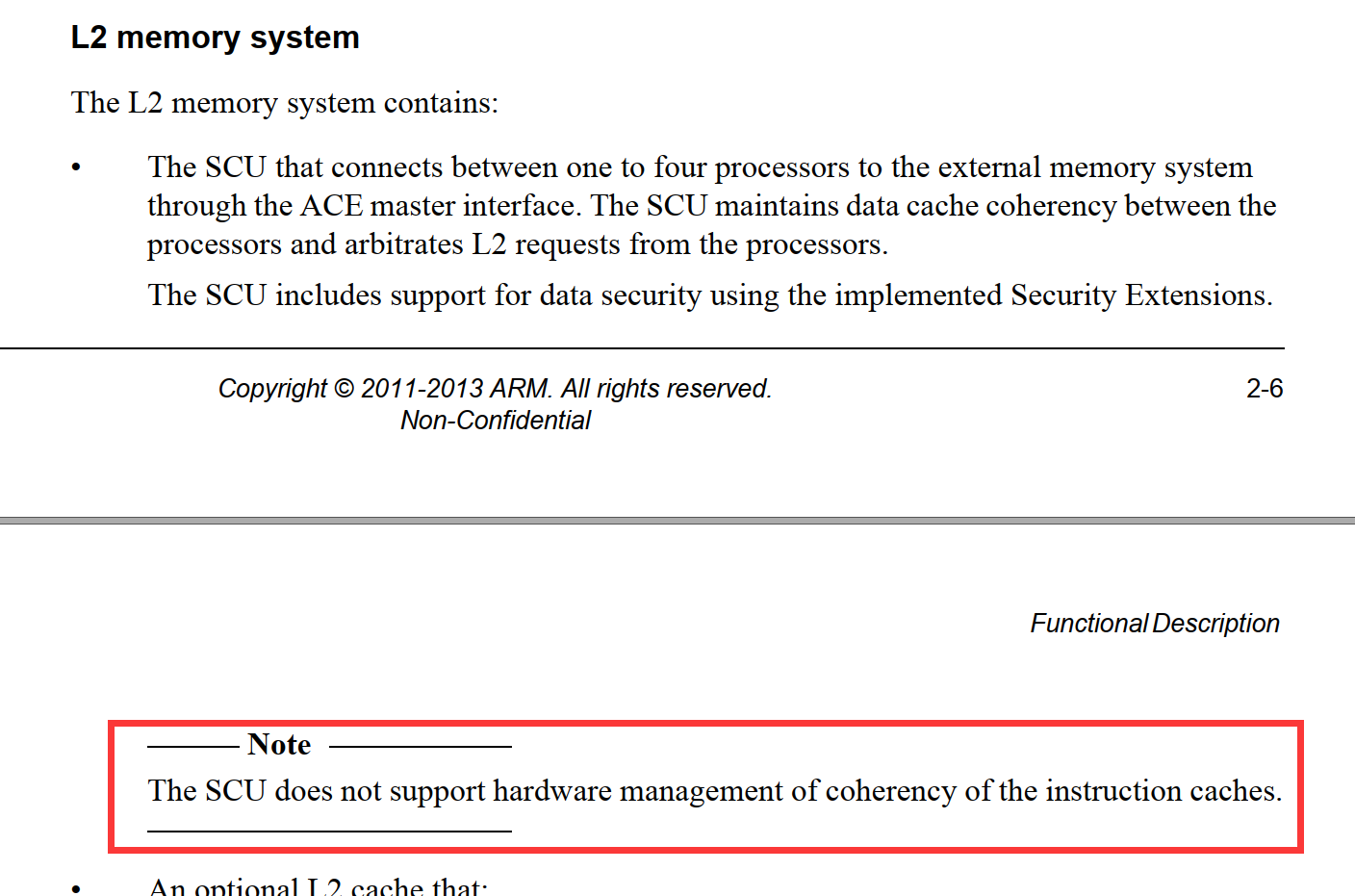

每个核都有自己的MMU和L1 Cache,此外还有一个SCU部件用于同步各个核的L1 DCache和L2 Cache中的数据一致性,也就是说L2 Cache也是个DataCache,而各个核中的L1 ICache数据的同步是不归SCU负责的,这个我们可以在手册中找到相关描述:

这个意思就是说各个核指令Cache同步需要由软件人员来负责,硬件只能保证数据Cache之间的同步。

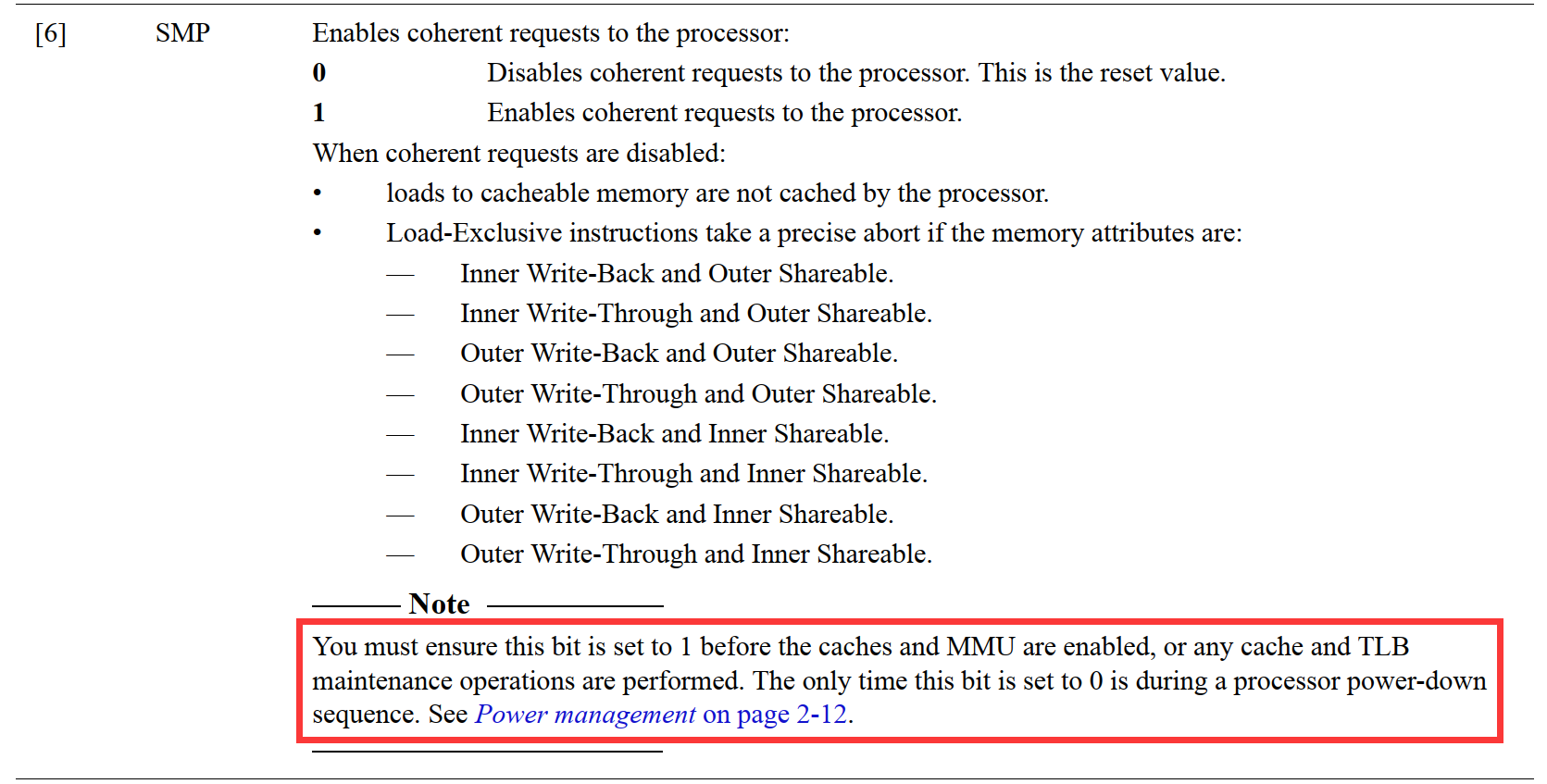

另外Cortex-A7架构中的L2 Cache是没法单独关闭的,必须和L1 DCache一起开关,这是通过两个系统控制器寄存器实现的。Auxiloiary Control Register这个辅助寄存器中的SMP位是控制是否使用硬件Cache一致性,并且手册中也明确写了再使能L1 Cache和MMU之前必须将这个SMP位置1:

系统控制寄存器System Control Register中的C位就是控制是否使能L1 DCache 和L2 Cache,并且说明了如果ACR.SMP为0的话,即使你将L1 DCache和L2 Cache打开的话那也是无效的:

L1指令Cache不受ACR.SMP位控制,可以单独打开和关闭。

2. SMP和AMP系统

如果想在多核硬件上运行操作系统,那么根据不同的需求,系统可以分为SMP和AMP两种模式。SMP系统是所有cpu核共同使用同一份操作系统镜像和硬件资源,比如内存、控制器等等。在SMP系统中虽然所有核是共享软硬件资源的,但是一般都有一个核是主核,负责管理其他核。AMP系统是每个核都运行自己的操作系统,并且一般需要对软硬件资源提前做划分,以确保每个核都能使用自己的软硬件资源,在需要和其他核进行数据交换时,通过某种核间通信的方式来交换数据。这些核上运行的操作系统可能是同一种也可能是不同种,甚至是不跑操作系统直接运行裸机程序。

在接下来的章节中我们将一起来学习如何开发SylixOS多核SMP BSP。

评论